電子工程網

標題: TI C2000系列TMS320F2837xD開發板硬件規格參數說明書(上) [打印本頁]

作者: Tronlong-- 時間: 2024-7-9 12:59

標題: TI C2000系列TMS320F2837xD開發板硬件規格參數說明書(上)

前 言

本文檔主要介紹TMS320F2837xD開發板硬件接口資源以及設計注意事項等內容��。

它是基于TI C2000系列TMS320F2837xD雙核C28x 32位浮點DSP + 紫光同創Logos/Xilinx Spartan-6 FPGA設計的開發板���。

核心板板載NOR FLASH和SRAM���,內部TMS320F2837xD與Logos/Spartan-6通過EMIF����、uPP����、I2C通信總線連接���,開發板接口資源豐富�,引出網口、CAN�����、USB�、ePWM、eQEP���、eCAP等接口。

核心板的DSP及FPGA的IO電平標準一般為3.3V����,上拉電源一般不超過3.3V����,當外接信號電平與IO電平不匹配時�����,中間需增加電平轉換芯片或信號隔離芯片��。按鍵或接口需考慮ESD設計,ESD器件選型時需注意結電容是否偏大��,否則可能會影響到信號通信��。

SOM-TL2837xF核心板

SOM-TL2837xF核心板板載DSP����、FPGA���、ROM��、RAM�、晶振�、電源、LED等硬件資源��,并通過工業級B2B連接器引出IO���。核心板硬件資源��、引腳說明����、電氣特性���、機械尺寸���、底板設計注意事項等詳細內容�,請查閱《SOM-TL2837xF核心板硬件說明書》。

圖 3

圖 4

圖 5

B2B連接器

評估底板采用4個廣瀨公司的工業級B2B連接器,共400pin�����,合高4.0mm�����。其中2個100pin母座B2B連接器(CON0A�����、CON0B)��,型號FX8-100S-SV(21)��,間距0.6mm,高度2.25mm;2個100pin公座B2B連接器(CON0C、CON0D)�,型號FX8-100P-SV1(91)����,間距0.6mm���,高度3.45mm�����。

圖 6

電源接口

CON2為12V直流輸入DC-417電源接口�,可接入外徑4.4mm��,內徑1.65mm電源插頭的電源適配器���。SW1為電源擺動開關���。

圖 7

設計注意事項:

VDD_12V_OVP(VDD_12V_MAIN)通過TPS54527DDA(DC-DC降壓芯片)輸出VDD_3V3_MAIN(VDD_3V3_SOM)供核心板使用���,通過另一路TPS54527DDA芯片輸出VDD_5V_MAIN供評估底板5V外設使用�。

圖 8

圖 9

圖 10

VDD_3V3_SOM在核心板內部未預留總電源輸入的儲能大電容��,底板設計時請在靠近B2B連接器位置放置儲能大電容����。

圖 11

BANK電壓配置電路

核心板內部已將FPGA端BANK0�����、BANK2、BANK3電平配置為3.3V�����。評估底板VDD_3V3_SOM向FPGA端BANK1提供3.3V供電。

圖 12

LED

評估底板具有LED0����、LED1����、LED2�、LED3、LED4���、LED5、LED6和LED7共8個LED���。

評估底板LED0為電源指示燈,上電自動點亮�。

圖 13

圖 14

LED1�����、LED2、LED3和LED4為DSP端用戶可編程指示燈�����,默認高電平點亮�����。

圖 15

圖 16

LED5、LED6����、LED7為FPGA端用戶可編程指示燈�,默認高電平點亮���。

圖 17

JTAG接口

CON4為DSP端TI Rev B JTAG仿真調試接口���,采用14pin簡易牛角座連接器�����,間距2.54mm���,可適配創龍科技的TL-XDS100V2�����、TL-XDS200和TL-XDS560V2仿真器。

圖 18

圖 19

CON5為FPGA JTAG仿真調試接口���,采用14pin簡易牛角座連接器,間距2.0mm�����。Logos系列FPGA可適配創龍科技的TL-PGMCable下載器�����,Spartan-6系列FPGA可適配創龍科技的TL-DLC10下載器。

圖 20

圖 21

設計注意事項:

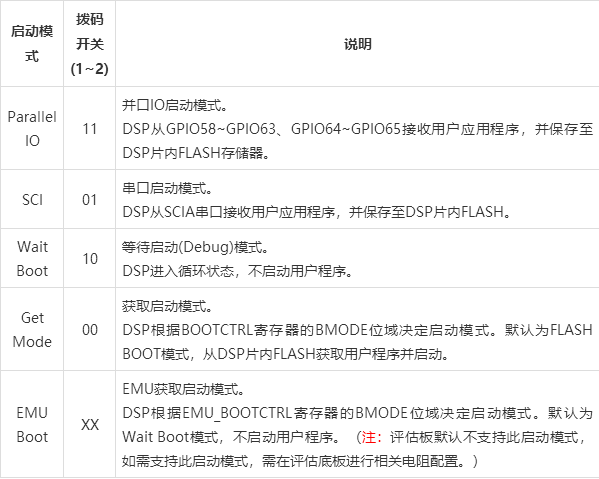

BOOT SET啟動方式選擇撥碼開關

SW2為DSP端2bit啟動方式選擇撥碼開關�����,ON為1����,相反為0���。評估板DSP端啟動方式具體說明如下����,常用啟動方式為Wait Boot和Get Mode模式。

表 1

備注:BOOT SET啟動選擇撥碼開關ON為1�,相反為0��,X代表任意值。

圖 22

圖 23

設計注意事項:

在核心板內部��,DSP端BOOTMODE引腳GPIO72��、GPIO84未配置上下拉電阻��。

BOOT[1:0]引腳如需上拉,請使用20K電阻上拉至3.3V���,如需下拉���,請使用2.2K電阻下拉至GND�。

由于BOOTMODE引腳與GPIO84、GPIO72(EMID12)引腳存在復用關系�,若使用該引腳外接設備時�����,請保證DSP在上電初始化過程中該引腳電平不受外接設備的影響,否則將會導致DSP無法正常啟動�����。

KEY

評估底板包含1個系統復位按鍵RESET(KEY3)���,3個DSP端用戶輸入按鍵USER KEY1(KEY1)��、USER KEY2(KEY2)����、USER KEY3(KEY4)��,3個FPGA端用戶測試按鍵USER KEY1(KEY5)���、USER KEY2(KEY6)和USER KEY3(KEY8)����,1個FPGA端FPGA Program按鍵(KEY7)��。

圖 25

RESET(KEY3)按鍵控制信號SYS_RESET_INPUT為DSP和FPGA的復位輸入引腳����,該復位信號不但復位DSP端所有寄存器��,還將復位DSP端所有調試環境。SYS_RESET_INPUT在核心板內部已上拉10K電阻至3.3V�����,設計底板無需再設計上拉電阻�。

圖 26

評估底板通過GPIO108引出用戶輸入按鍵KEY1,通過GPIO109引出用戶輸入按鍵KEY2�,通過GPIO110引出用戶輸入按鍵KEY4�,引腳均上拉4.7K電阻至VDD_3V3_MAIN�。

圖 27

評估底板通過FPGA端IO引腳引出用戶輸入按鍵KEY5、KEY6�、KEY8����,引腳均上拉4.7K電阻至VDD_3V3_MAIN���。

圖 28

KEY7按鍵控制FPGA_RST_N_KEY(Spartan-6對應為FPGA_PROGRAM_B_KEY)信號。FPGA_RST_N_KEY為核心板FPGA端的邏輯復位信號����,默認情況請懸空處理���。

圖 29

| 歡迎光臨 電子工程網 (http://www.qingdxww.cn/) |

Powered by Discuz! X3.4 |

主站蜘蛛池模板:

狠狠色依依成人婷婷九月

|

日韩高清伦理片中字在线观看

|

免费在线视频成人

|

夜夜夜夜曰天天天天拍国产

|

亚洲视频免费在线播放

|

久久久精品2018免费观看

|

欧美日韩一级黄色片

|

伊人青青草

|

成人午夜视频在线观

|

欧美成人免费高清二区三区

|

一级片免费在线播放

|

亚洲专区在线视频

|

久草综合视频在线

|

成人毛片18女人毛片免费96

|

青青免费在线视频

|

日本中文字幕高清

|

落跑甜心电视剧全集免费观看在线

|

亚洲乱视频

|

国产精品亚洲一区二区麻豆

|

视频一区中文字幕

|

亚洲综合亚洲综合网成人

|

久久精品蜜芽亚洲国产a

|

在线视频欧美精品

|

欧美成人久久一级c片免费

欧美成人久久久免费播放

欧美成人精品在线

|

99在线热视频只有精品免费

|

九九香蕉|

成人97在线观看免费高清

|

在线看亚洲

|

亚洲欧美另类视频

|

成人黄色在线观看视频

|

日本欧美国产

|

免费人成在线水蜜桃视频

|

97免费视频免费视频

|

国产野花视频天堂视频免费

|

91最懂男人的午夜社区

|

91亚洲自偷手机在线观看

|

天天操综

|

国产麻豆剧传媒精品好看的片

|

毛片免费毛片一级jjj毛片

|

亚洲综合成人在线

|

99久久精品免费看国产情侣

|