|

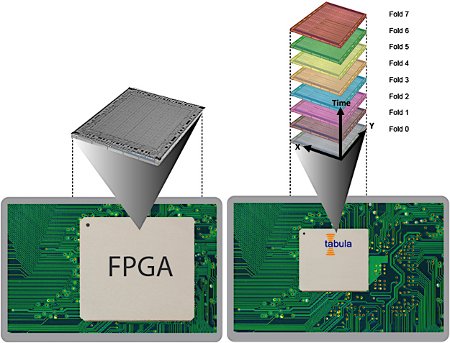

| Teig: I asked myself what if there was a new class of programmable device beyond FPGA. |

|

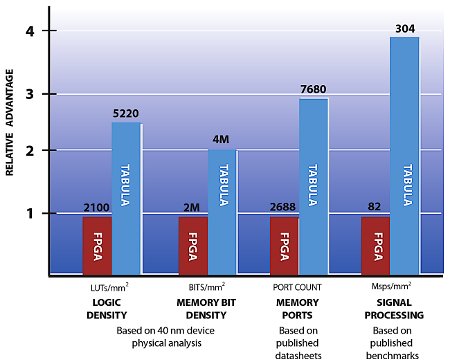

| Figure 1: Tabula claims its architecture delivers significant performance and logic density advantages over traditional FPGAs. |

|

| Figure 2: Spacetime architecture creates folds of circuit portions in time and running at frequencies up to 1.6GHz to allow trading of time with space and performance with density. |

| 歡迎光臨 電子工程網(wǎng) (http://www.qingdxww.cn/) | Powered by Discuz! X3.4 |