|

上個(gè)月,賽靈思(Xilinx)宣布其Kintex-7 325T FPGA開(kāi)始發(fā)貨,這是業(yè)界推出最快的28nm新一代可編程邏輯器件產(chǎn)品。近日,賽靈思全球高級(jí)副總裁和賽靈思亞太區(qū)執(zhí)行總裁湯立人先生及賽靈思公司亞太區(qū)市場(chǎng)及應(yīng)用總監(jiān)張宇清先生來(lái)京介紹了該公司的最新技術(shù)與優(yōu)勢(shì)。 湯立人介紹說(shuō),Kintex-7 325T器件已經(jīng)面市并提供樣品,首款Kintex-7開(kāi)發(fā)板已經(jīng)面市,AXI4 IP和目標(biāo)參考設(shè)計(jì)開(kāi)發(fā)完畢并投入運(yùn)行,ISE 13.1設(shè)計(jì)套件已經(jīng)針對(duì)7系列設(shè)計(jì)開(kāi)放。7系列開(kāi)發(fā)板與套件供貨比以往更快,更多開(kāi)發(fā)板正在投放到現(xiàn)場(chǎng)或者抵達(dá)客戶手中。ISE 13.1設(shè)計(jì)套件發(fā)布得非常成功,發(fā)布后3周內(nèi)的下載數(shù)量比12版本同期高出60%。 此次賽靈思把芯片和開(kāi)發(fā)板帶到了現(xiàn)場(chǎng),表示已經(jīng)為市場(chǎng)做好了準(zhǔn)備。他說(shuō),全球很多客戶都在下單,安捷倫是第一個(gè)客戶。有很多客戶已經(jīng)看過(guò)賽靈思的樣片,他們都認(rèn)為,7系列對(duì)他們以后的開(kāi)發(fā)有很大的幫助。

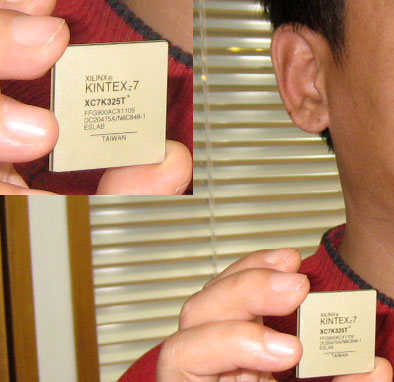

筆者手中的Kintex-7 325T

首款Kintex-7開(kāi)發(fā)板 賽靈思的7系列包括四個(gè)系列產(chǎn)品:VIRTEX、KINTEX ARTIX,以及上個(gè)月發(fā)布的ZYNQ,一年多來(lái)賽靈思推出了四個(gè)系列的28nm芯片,比以往的開(kāi)發(fā)速度更快。 張宇清介紹說(shuō),28nm的面世不是偶然的。如今市場(chǎng)變幻多端,客戶的需求不會(huì)因?yàn)楣⿷?yīng)商開(kāi)發(fā)芯片的難度加大、性能提高就給予你更充分的準(zhǔn)備時(shí)間,他們希望芯片廠商盡快把產(chǎn)品推向市場(chǎng)。同時(shí),功耗和性能之間要取一個(gè)平衡點(diǎn),必須在這沖突的兩者當(dāng)中采取一定程度的妥協(xié)。 在設(shè)計(jì)工具方面,客戶希望能夠提高設(shè)計(jì)團(tuán)隊(duì)的生產(chǎn)力。要提高生產(chǎn)效率、縮短IP開(kāi)發(fā)過(guò)程,唯一的方法就是標(biāo)準(zhǔn)化。賽靈思通過(guò)三個(gè)行業(yè)標(biāo)準(zhǔn)而實(shí)現(xiàn):標(biāo)準(zhǔn)互連、標(biāo)準(zhǔn)封裝和標(biāo)準(zhǔn)安全。 首先是互聯(lián)標(biāo)準(zhǔn)。賽靈思與合作伙伴合作研發(fā)推出第三代總線架構(gòu),這是一個(gè)標(biāo)準(zhǔn)的互聯(lián)方式,它的好處體現(xiàn)在如果符合這個(gè)標(biāo)準(zhǔn),通過(guò)IP驗(yàn)證后,所有IP可以兼容。不但是賽靈思的IP,包括ARM公司的伙伴和其他客戶的IP,只要遵循這個(gè)標(biāo)準(zhǔn)就可以兼容。 其次,賽靈思提供一個(gè)IP封裝器。無(wú)論是賽靈思的IP還是伙伴的IP,封裝后就具有一致性。IP聯(lián)盟計(jì)劃里的成員使用這個(gè)IP封裝器,每家公司的軟件接口就一致,這樣兼容就會(huì)非常容易,在設(shè)計(jì)的時(shí)候速度也會(huì)非常快。 張宇清說(shuō),賽靈思推出IP封裝器的時(shí)候是希望分段推出,賽靈思不希望一下子全部推出給所有客戶,賽靈思先推出給最緊密的合作伙伴,因?yàn)檫@些伙伴已經(jīng)跟賽靈思非常緊密了,從5系列、4系列就已經(jīng)開(kāi)始合作了。首先在他們中間驗(yàn)證,明年再把它推向市場(chǎng)。賽靈思現(xiàn)在全球有300個(gè)伙伴,再加上賽靈思的客戶,以及ARM的伙伴,廠商總數(shù)就很多了。 最后是行業(yè)標(biāo)準(zhǔn)IP-XACT。 這個(gè)標(biāo)準(zhǔn)是IEEE推動(dòng)的,它所有的IP保護(hù)也要標(biāo)準(zhǔn)化,這個(gè)支持AXI BFM,因?yàn)樗墓δ芗用芏际菢?biāo)準(zhǔn),賽靈思在ISE13.3可以支持。標(biāo)準(zhǔn)化可以提升使用效率。很多時(shí)候IP是復(fù)用的,如果沒(méi)有標(biāo)準(zhǔn)化就要花很多的時(shí)間去做復(fù)用。 符合這樣的需求,賽靈思首先推出的是終端產(chǎn)品系列,其性能非常強(qiáng)大,比現(xiàn)在的Virtex-6強(qiáng)大許多。它的密度和容量大,28nm器件有32個(gè)收發(fā)器,每個(gè)收發(fā)器可以跑到12.5G。它存儲(chǔ)的速度是業(yè)界最快的。K325T功耗很低,內(nèi)含功耗模塊設(shè)計(jì),功耗與Virtex-6相比降低了一半。 7系列的一個(gè)重要特點(diǎn)就是它的架構(gòu)從低端到高端、中端三個(gè)系列是完全統(tǒng)一的,這樣可以方便IP移植。你可以先用Virtex-7做設(shè)計(jì),將來(lái)要用7系列做一個(gè)高端設(shè)計(jì),或如果將來(lái)設(shè)計(jì)是希望低功耗也可以用Virtex-7做設(shè)計(jì),然后再轉(zhuǎn)向Kintex-7,移植非常容易。 統(tǒng)一架構(gòu)是一個(gè)好的想法,以前賽靈思一直都沒(méi)有去做的原因是,以前的工藝要求采用低端的架構(gòu)才能夠達(dá)到最高的效益。但是在28nm工藝下,本身電子管就很小,如果用低端架構(gòu),對(duì)整個(gè)芯片功耗各方面的影響沒(méi)有太大的影響。另外,賽靈思不進(jìn)入很低端的市場(chǎng),不需要像手機(jī)芯片那樣低功耗的產(chǎn)品。 采用統(tǒng)一架構(gòu)后,IP移植會(huì)方便很多,一般可以減少一半的時(shí)間,比如一個(gè)設(shè)計(jì)六個(gè)月,現(xiàn)在用三個(gè)月就可以做完移植。因?yàn)榻y(tǒng)一架構(gòu)也要選擇一個(gè)架構(gòu),是選擇低端還是高端?賽靈思選擇了高端器件的架構(gòu)。 高端應(yīng)用中,用戶需要研發(fā)支持高帶寬、高容量、大規(guī)模的并行功能。在設(shè)計(jì)工具上的需求是,身處異地的團(tuán)隊(duì)能夠共同進(jìn)行一個(gè)項(xiàng)目設(shè)計(jì)。賽靈思不僅支持多團(tuán)隊(duì)共同設(shè)計(jì),還支持部分可重配置,就是可以把FPGA部分功能實(shí)施轉(zhuǎn)換,而不需要斷電,這可以降低整個(gè)FPGA的功耗。這些領(lǐng)域包括一些新興的應(yīng)用,如智能電網(wǎng)、醫(yī)療成像等。 針對(duì)這類(lèi)高端應(yīng)用,賽靈思的方案是業(yè)界領(lǐng)先的Virtex-7。它包含5280個(gè)DSP(去年宣布的時(shí)候是4000個(gè)),收發(fā)器數(shù)目也增加到96個(gè),達(dá)到了前所未有的高度。在高端器件里,賽靈思的收發(fā)器有一部分支持到28Gbps。這里應(yīng)用了賽靈思相當(dāng)多的尖端技術(shù),包括堆疊硅片互聯(lián)技術(shù)。 軟件方面,PlanAhead幫助同一個(gè)項(xiàng)目的多個(gè)工程師在不同的地點(diǎn)進(jìn)行工作。他們?cè)O(shè)計(jì)一個(gè)項(xiàng)目里不同的模塊,可以很容易用PlanAhead把整個(gè)設(shè)計(jì)歸納成一體,其優(yōu)勢(shì)在于時(shí)序保持,也就是鎖定一塊時(shí)序,最后集成時(shí)不需要時(shí)序有任何的改變。另外還有設(shè)計(jì)保存。以前沒(méi)有時(shí)序保持的時(shí)候,每次跑布線候時(shí)序要做改變,要重新看設(shè)計(jì)時(shí)序。 低端應(yīng)用(如工業(yè)自動(dòng)化、消費(fèi)類(lèi)電子)要求產(chǎn)品上市快、功耗低,同時(shí)性能也不能太差。 針對(duì)這些應(yīng)用,賽靈思Artix系列的收發(fā)器增加到了16個(gè)(以前是10個(gè)),而且速度從3.75G提升到6.6G。Artix器件可以輕松應(yīng)對(duì)低端大批量、低功耗市場(chǎng),其性能超越了低端FPGA,具備以往一些高端器件才有的功能。AMS (敏捷的混合信號(hào))模塊可以很敏捷做電平監(jiān)控,包括片上電壓和熱傳感器的檢測(cè),這些功能以前在高端器件上才會(huì)有,現(xiàn)在7系列全線產(chǎn)品和Artix都有這個(gè)功能。 所有7系列高、中、低端產(chǎn)品配上賽靈思的軟件都可以實(shí)現(xiàn)功耗降低。與思競(jìng)爭(zhēng)對(duì)手相比,在沒(méi)有用動(dòng)態(tài)重配置的情況下他們的功耗比賽靈思大的多,他們必須要用動(dòng)態(tài)重配置才能勉強(qiáng)接近賽靈思,但仍有30%的差距。 ZYNQ系列發(fā)布時(shí)在國(guó)內(nèi)引起了轟動(dòng),博客和網(wǎng)站對(duì)這個(gè)器件都流露出非常驚訝的反應(yīng),因?yàn)樗谔幚砥黝I(lǐng)域中是前所未有的:它既不屬于FPGA,也不是單純的處理器,而是兩者合一。實(shí)際上它還集成了DSP,所以它是DSP、FPGA和處理器的三合一。其應(yīng)用主要包括駕駛員輔助、工廠自動(dòng)化、廣播級(jí)、監(jiān)控和雷達(dá)等。 ZYNQ的優(yōu)勢(shì)主要發(fā)揮在工廠自動(dòng)化方面。跟多芯片方案相比,它在性能、功耗、甚至成本上都會(huì)有很大的優(yōu)勢(shì),而且具備靈活性和可擴(kuò)展性(可編程能力)。 ZYNQ是一個(gè)新類(lèi)別的產(chǎn)品,它是多用途的,它可以符合不同產(chǎn)業(yè)的需求同時(shí)保持它的性能和低功耗,最重要是縮短了產(chǎn)品的上市時(shí)間。它是在傳統(tǒng)可編程行業(yè)基礎(chǔ)上的一大飛躍,是真正意義上的SoC。 賽靈思也推出在ZYNQ這種FPGA加處理器的架構(gòu)之下新的設(shè)計(jì)方法。一般來(lái)說(shuō)是軟件工程師先設(shè)計(jì),設(shè)計(jì)好算法,把它交付于硬件工程師去實(shí)施,有問(wèn)題再重新返回到軟件工程師處做修改。現(xiàn)在賽靈思可以讓設(shè)計(jì)流程的硬件和軟件同時(shí)進(jìn)行,也就是說(shuō)今天軟件在設(shè)計(jì)的時(shí)候可以在開(kāi)發(fā)板上直接看到軟件設(shè)計(jì)的算法出來(lái)的效果,意味著軟件工程師以后也在一定程度上可以去做硬件的事情,設(shè)計(jì)一個(gè)FPGA,以往他要交給FPGA工程師去做,現(xiàn)在他自己可以做了,這是設(shè)計(jì)生產(chǎn)力上一個(gè)很大的轉(zhuǎn)變。 |